m基于UW序列的数据帧检测,帧同步verilog实现,含testbench

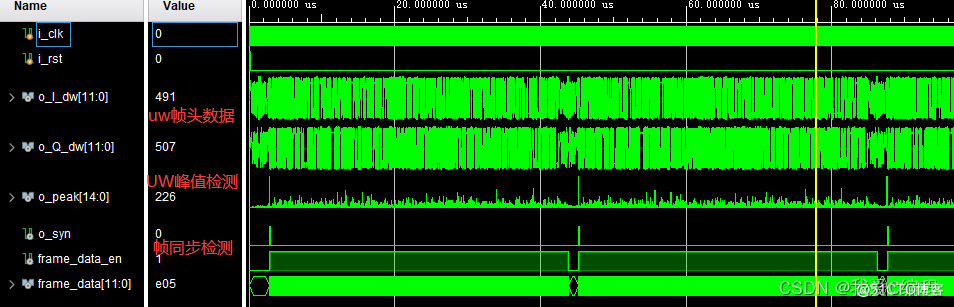

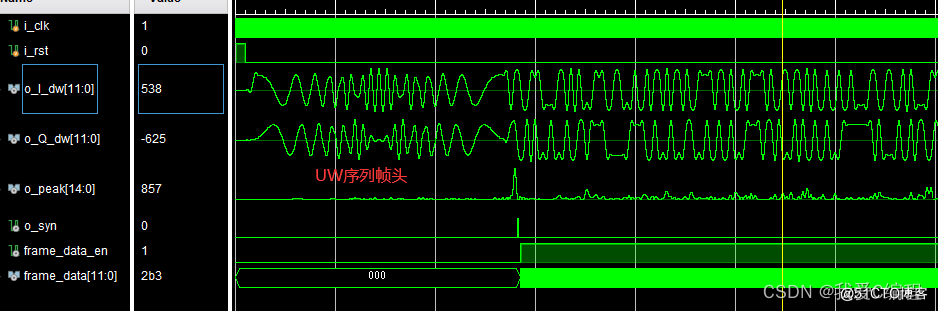

1.算法仿真效果

本系统进行了Vivado2019.2平台的开发,仿真结果如下所示:

2.算法涉及理论知识概要

UW序列是一种特殊类型的伪随机二进制序列,通常用于数据帧检测和帧同步。UW序列具有以下特性:

平衡性:UW序列中的1和0的数量大致相等,确保序列具有良好的自相关性。

低互相关:不同UW序列之间的互相关性非常低,减少误检测的可能性。

长周期:UW序列的周期非常长,保证在数据传输过程中不会重复。

在数据帧检测中,发送端会将数据帧的头部与UW序列进行异或操作,接收端通过检测UW序列的出现来识别数据帧的起始位置和帧同步。

数据帧通常由头部(header)、数据(payload)和尾部(tail)组成。在发送端,数据帧的头部会与UW序列进行异或操作,然后发送给接收端。接收端会通过以下过程来检测数据帧的起始位置和帧同步:

接收数据流并与UW序列进行互相关运算,得到互相关结果R。

将R与阈值进行比较,如果超过阈值,则认为找到了帧同步。

1 发送端实现

在发送端,首先确定数据帧的格式,包括头部、数据和尾部的长度。然后,选择一个合适的UW序列,并将数据帧的头部依次与UW序列进行异或操作。将得到的带有UW序列的头部发送给接收端。

2 接收端实现

在接收端的FPGA中,实现数据帧检测和帧同步需要进行以下步骤:

选择UW序列:在接收端选择与发送端使用的UW序列相同的UW序列。

互相关运算:将接收到的数据流与选定的UW序列进行互相关运算,得到互相关结果R。

阈值判定:将R与预先设定的阈值进行比较。阈值的选取要基于信噪比和系统性能考虑,通常通过实验来确定。

帧同步:当R超过阈值时,表示找到了帧同步,接下来可以开始解析数据帧。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/07/24 21:40:51

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

// Inputs

reg i_clk;

reg i_rst;

// Outputs

wire [11:0] o_I_dw;

wire [11:0] o_Q_dw;

wire[14:0] o_peak;

wire o_syn;

wire frame_data_en;

wire [11:0] frame_data;

// Instantiate the Unit Under Test (UUT)

UW_1_sycn uut (

.i_clk (i_clk),

.i_rst (i_rst),

.o_I_dw (o_I_dw),

.o_Q_dw (o_Q_dw),

.o_peak (o_peak),

.o_syn (o_syn),

.frame_data_en(frame_data_en),

.frame_data (frame_data)

);

initial begin

// Initialize Inputs

i_clk = 1;

i_rst = 1;

// Wait 100 ns for global reset to finish

#100

i_rst = 0;

// Add stimulus here

end

always #5 i_clk=~i_clk;

endmodule