同步时序和异步时序电路

同步时序电路

同步时序电路的组成规则:一个电路是同步时序电路,若它由相互连接的电路元件构成,则需要满足以下条件:

- 每一个电路元件是寄存器/组合电路

- 至少一个电路元件是寄存器

- 所有寄存器都接收同一个时钟信号

- 每个环路至少包含一个寄存器

最简单的同步时序电路

最简单的同步时序电路

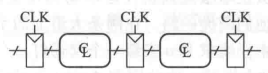

同步时序逻辑电路的流水线形式

同步时序逻辑电路的流水线形式

异步时序电路

非同步时序电路:异步电路

同步和异步电路

理论上,异步电路设计比同步电路设计更通用

因为:系统时序不受时钟控制的寄存器约束

类比→用任意电压的模拟电路比数字电路更通用;可使用各种反馈的异步电路比同步电路更通用

但,同步电路比异步电路更好设计;数字电路比模拟电路更容易。

实际上,几乎所有的系统本质上都是同步的。(两不同时钟的系统间通信、任意时刻接收输入,异步电路也重要)

总之,研究异步电路可能有利于改进同步电路

有限状态机

设计有限状态机的步骤:

1.确定输入输出

2.画状态图

3.对Moore型状态机:

①写状态转换表

②写输出表

4.对Mealy型状态机:

写出组合的状态转换表和输出表

5.选择状态编码(影响硬件设计)

6.为下一状态和输出逻辑写布尔表达式

7.画出电路草图

时序逻辑的时序

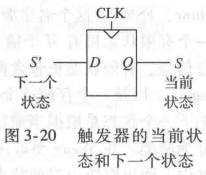

时钟沿对D采样:触发器在时钟沿上升沿将输入D复制到输出Q