从零开始制作示波器--原理图设计之CIS库制作-0-CIS库建立-FPGA元件库建立(xcku5p)(cadence-orcad16.6)

设计中拟采用FPGA+zynq的方案,其中FPGA选型为:XCKU5P-FFVB676AAZ,这是一款676引脚的kintex-U+系列FPGA,此部分介绍其原理图库设计。

1、建元件

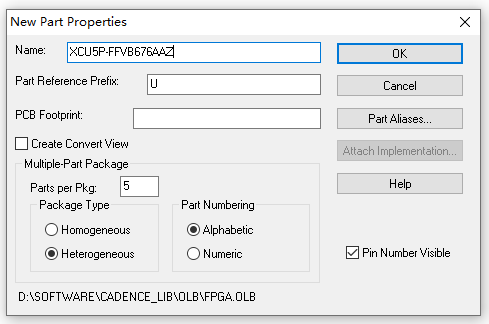

先建立一个元件,里面小元件个数随意写个值(后期可更改),其中“package Type”,“Part Numbering”按默认就行。“package Type”两个选项的意思分别是:封装相同(另一选项为:封装不同),此处选不同封装。“Part Numbering”两个选项:按字母表排序、按数字排序(默认按字母排序)。

建好的元件如下图所示(未绘制符号)

2、原理图符号绘制

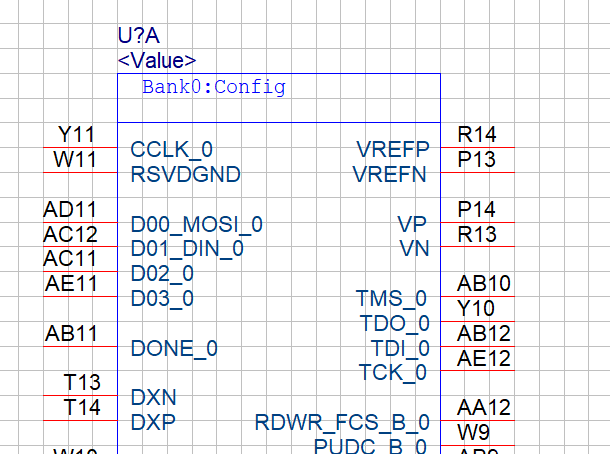

2.1、Bank0绘制

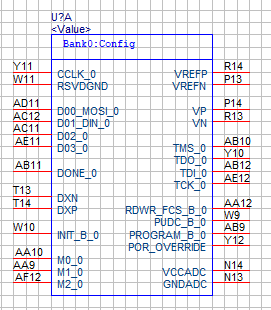

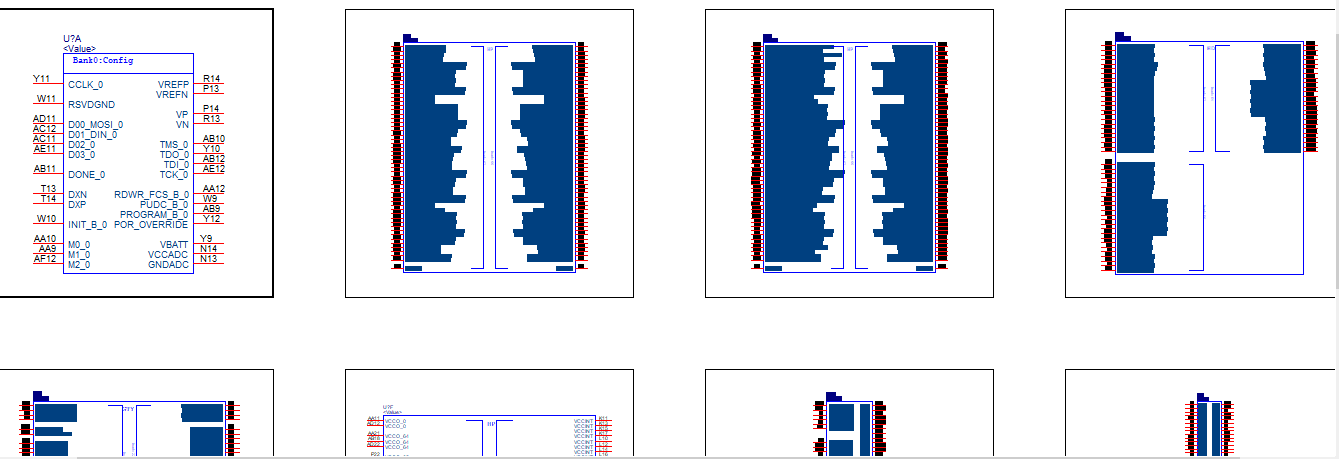

此部分为FPGA的配置bank,在以前会有这样一个疑问:怎么知道每个Pin脚需要标识的内容,怎么知道每个pin所在的bank?以前想到的是从vivado中读取,其实xilinx提供了直接的Pin脚定义表(https://www.xilinx.com/support/package-pinout-files.html),此处按表设计bank0,设计安城的Bank0如下图所示:

(对齐前)

(对齐后)

到此bank0初步制作完成,对于每个引脚的特性,此处都为默认值,后期需根据datasheet进一步完善,因当前任务为搭建框架,对细化的部分暂不做处理,此部分需后期完善。

2.2、其他bank制作。

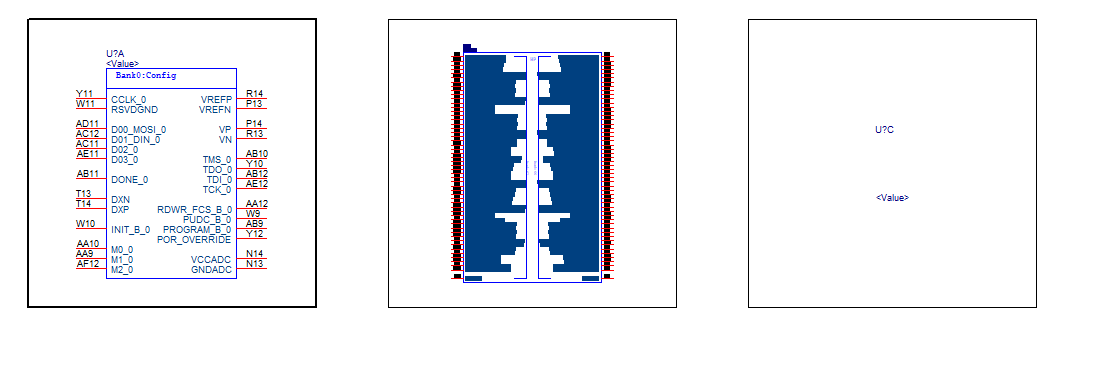

按bank0的方式制作其他bank,制作完成bank66、67如图所示:

初步制作完成的原理图库如下:

到此步骤,原理图符号已经可以使用了,若是粗放点的,原理图符号算是设计完成了,但是止步于此会有以下几个弊端:

1)、每个引脚内部特性未作表示,无法进行DRC检查。

2)、未标识关键指标,设计原理图时需要不断翻阅datasheet查看、确定参数。

3)、原理图评审时,若有详细参数标识,更能有助于发现问题。

基于以上几点,此原理图库设计还需进一步进行。