m基于双UW序列的数据帧检测verilog实现,含testbench

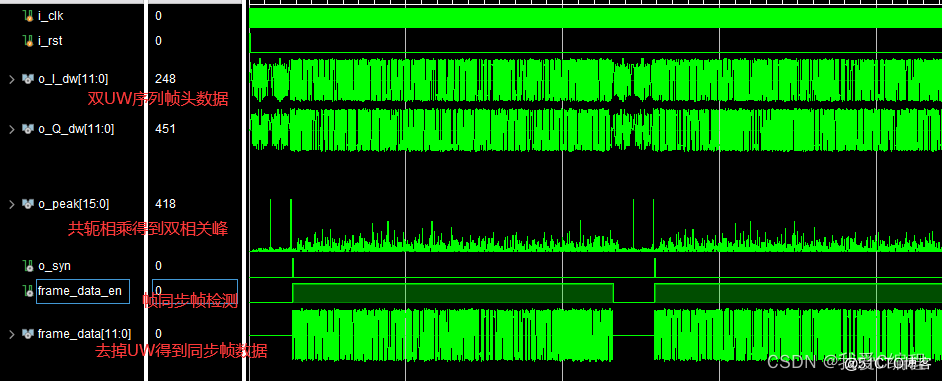

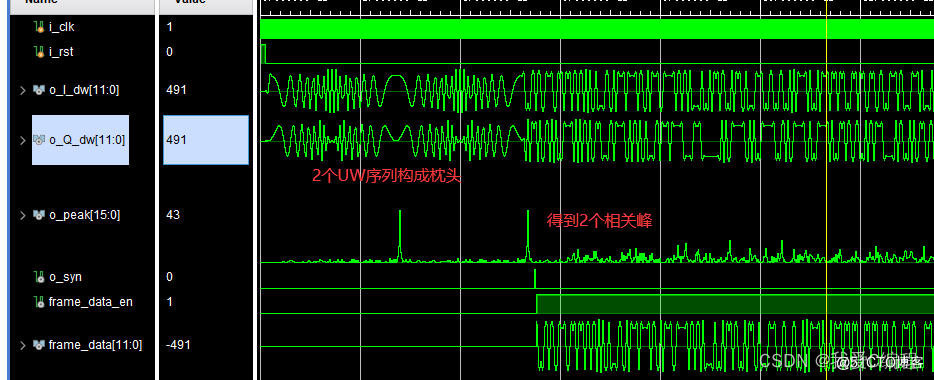

1.算法仿真效果

本系统进行了Vivado2019.2平台的开发,仿真结果如下:

2.算法涉及理论知识概要

"基于双UW序列的数据帧检测Verilog实现"是一种数字电路设计方案,旨在实现数据通信中的数据帧检测功能。该方案采用双UW(Unambiguous Word)序列作为同步序列,通过硬件描述语言Verilog来设计和实现数据帧检测模块。数据帧检测是通信系统中重要的环节,用于正确识别接收到的数据帧的开始位置,从而确保数据的正确传输和解码。

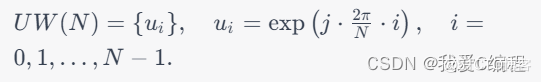

双UW序列是一种特殊的同步序列,具有无歧义性,用于同步接收端的时钟与发送端的时钟。它是由两个UW序列连接而成的,其中UW序列定义如下:

在通信系统中,发送端将数据划分为多个数据帧,并在每个数据帧的开始位置插入同步序列,以便接收端正确识别数据帧的边界。数据帧检测的目标是在接收到的信号中找到同步序列,从而确定数据帧的起始位置。双UW序列作为一种特殊的同步序列,可以通过在接收端进行相关运算来实现数据帧检测。

接收端从信道中接收到数字信号,并对信号进行采样和量化,得到数字信号样本。

接收端利用双UW序列对接收信号进行相关运算。相关运算的目的是在接收信号中找到与双UW序列最相似的部分,从而确定数据帧的起始位置。根据相关运算的结果,接收端判断是否检测到双UW序列。如果检测到双UW序列,则表示成功找到数据帧的起始位置;否则,表示数据帧未被正确检测。

一旦成功检测到数据帧的起始位置,接收端可以开始对数据帧进行解码和处理。 "基于双UW序列的数据帧检测Verilog实现"在数字通信系统中有广泛的应用。它可以用于各种数据传输场景,如无线通信、有线通信、局域网等。数据帧检测是数据通信中非常关键的一环,它直接影响到数据的可靠传输和正确解码。因此,这种Verilog实现方案可以用于各种通信设备和系统中,提高数据通信的可靠性和稳定性。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/07/24 21:40:51

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

// Inputs

reg i_clk;

reg i_rst;

// Outputs

wire [11:0] o_I_dw;

wire [11:0] o_Q_dw;

wire[15:0] o_peak;

wire o_syn;

wire frame_data_en;

wire [11:0] frame_data;

// Instantiate the Unit Under Test (UUT)

UW_2_sycn uut (

.i_clk (i_clk),

.i_rst (i_rst),

.o_I_dw (o_I_dw),

.o_Q_dw (o_Q_dw),

.o_peak (o_peak),

.o_syn (o_syn),

.frame_data_en(frame_data_en),

.frame_data (frame_data)

);

initial begin

// Initialize Inputs

i_clk = 1;

i_rst = 1;

// Wait 100 ns for global reset to finish

#100

i_rst = 0;

// Add stimulus here

end

always #5 i_clk=~i_clk;

endmodule