计算机组成与体系结构 2 简单的计算机系统MARIE

2 简单的计算机模型MARIE

总线

分类1

- 点对点总线

- 多点总线

分类2

- 数据线(并行 /串行)

- 控制线(设备使用总线的权限 /传输总线请求的应答 /确认中断和时钟同步信号)

- 地址线

- 电源线

主线仲裁机制

对于多个主控设备的系统,为某些主控设备设置优先级别,又保证各个主控设备都有机会使用总线

- 菊花链仲裁方式:从最高优先级到最低(优先级低的设备可能被“饿死”,简单但不公平)

- 集中式并行仲裁方式:仲裁控制器(所有请求都集中在一个仲裁器上,导致瓶颈)

- 采用自选择的分配式仲裁方式:设备自己决定

- 采用冲突检测的分配式仲裁方式:如果多个请求者同时请求资源,系统会进行冲突检测,以确定哪个请求可以被满足(常见)

时钟

控制指令执行速度的内部时钟

指令的性能通常是通过时钟周期(时钟频率的倒数)的数目(而不是秒)来测量的

存储器

存储器通常使用符号 L x W(长 x 宽)表示

e.g. 4M x 8 = 222 x 8, (字节)地址:0 ~ 222-1

单个存储器模块只能串行访问(每次只能执行一次存储器访问); 交叉存储器把存储器分成多个模块,多个模块可以同时访问。

模块的数量取决于有多少个可寻址单元,n个模块 = n路交叉

高位交叉:使用地址的高位选择模块

低位交叉:使用地址的低位选项模块

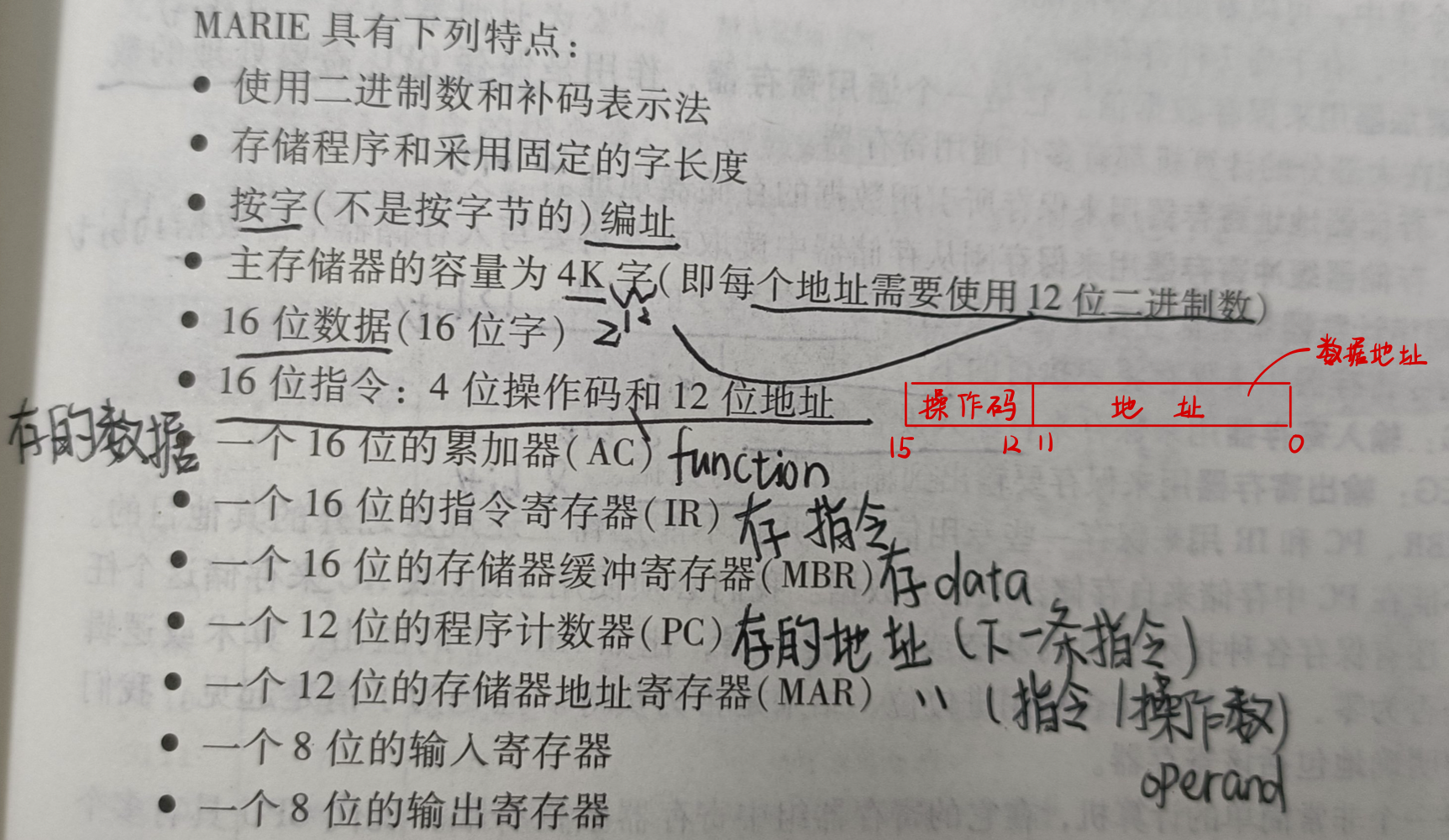

MARIE特点

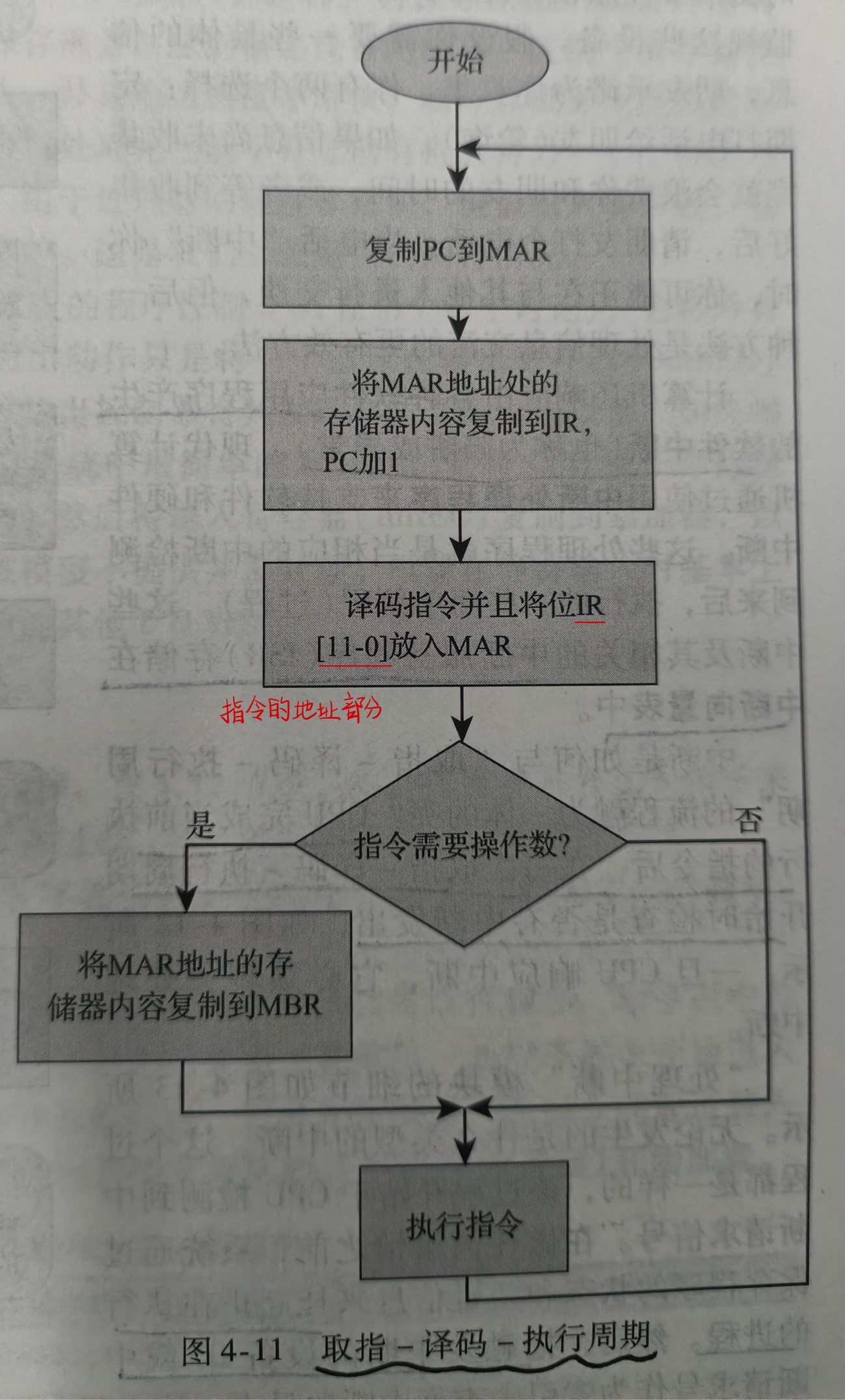

指令执行过程

寄存器与指令集

Load X:将地址位X的存储单元中的内容装入AC

MAR <- X

MBR <- M[MAR]

AC <- MBR

Store X:将AC中的内容存储到地址X的存储单元中

MAR <- X, MBR <- AC

M[MAR] <- MBR

Add X:将地址X中的内容和AC中的内容相加,将结果存到AC中

MAR <- X

MAR <- M[MAR]

AC <- AC + MBR

Subt X:从AC中减去地址X中的内容,将结果存到AC中

MAR <- X

MAR <- M[MAR]

AC <- AC - MBR

Input

AC <- InREG

Output

OutREG <- AC

Halt:停止程序的执行

Skipcond:有条件地跳过下一条指令

If IR[11-10] = 00 then

If AC < 0 then PC <- PC + 1

else If IR[11-10] = 01 then

If AC = 0 then PC <- PC + 1

else If IR[11-10] = 10 then

If AC > 0 then PC <- PC + 1

Jump X:无条件转向给定地址X

PC <- X

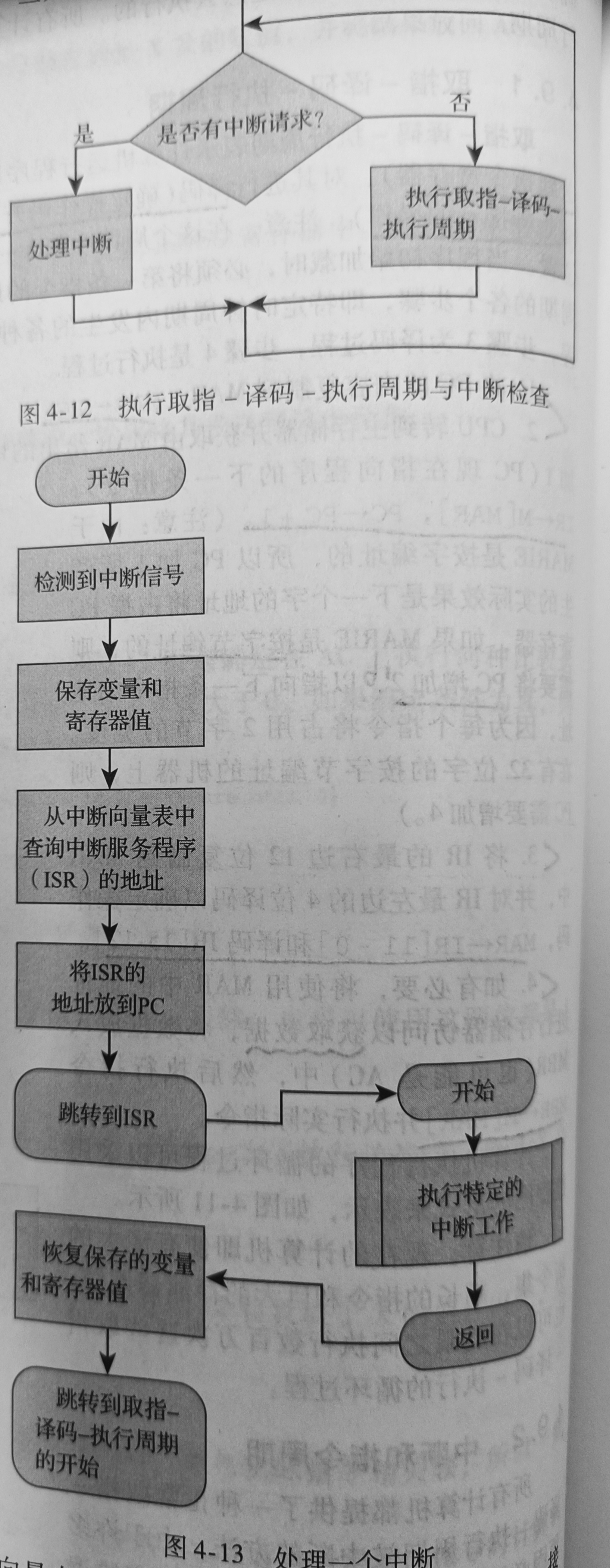

中断

- 硬件中断

- 软件中断(陷阱 /异常)

中断产生原因:

程序错误、硬件错误、I/O完成、用户中断、定时器中断

中断屏蔽:使用标志寄存器中的特殊中断屏蔽位暂停非关键中断(可屏蔽中断)

不可屏蔽中断不能暂停